# TSG65N068CE

Taiwan Semiconductor

#### **FEATURES**

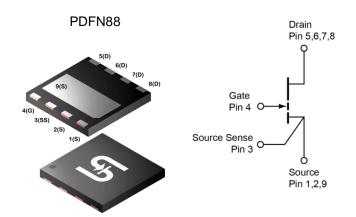

- 650 V enhancement mode power transistor

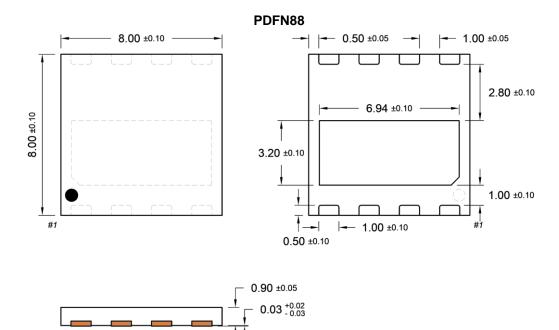

- Bottom-cooled, 8x8 mm PDFN package

- RDS(on)(Typ) = 50 mΩ

- IDS(max) = 30 A

- Simple gate drive requirements (0 V to 6 V)

- Transient tolerant gate drive (-20 V / +10 V)

- High switching frequency (> 1 MHz)

- Fast and controllable fall and rise times

- Reverse conduction capability

- Zero reverse recovery loss

- Source Sense (SS) pin for optimized gate drive

- ROHS Compliant

- Halogen-free

#### **APPLICATIONS**

- Bridgeless Totem Pole PFC

- Consumer, Industrial and Datacenter High Density Power Supply

- High Power Adapters

- LED Lighting Drivers

- Solar Inverter

- Uninterruptable Power Supplies

- Appliance and Industrial Motor Drives

- Laser Drivers

- Wireless Power Transfer

| KEY PERFORMANCE PARAMETERS   |                      |       |      |  |

|------------------------------|----------------------|-------|------|--|

| PARAMETER                    |                      | VALUE | UNIT |  |

| V <sub>DS</sub>              |                      | 650   | V    |  |

| R <sub>DS(on)</sub><br>(max) | V <sub>GS</sub> = 6V | 68    | mΩ   |  |

| Qg                           |                      | 6.7   | nC   |  |

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25°C unless otherwise noted)      |                 |             |      |  |  |

|------------------------------------------------------------------------------|-----------------|-------------|------|--|--|

| PARAMETER                                                                    | SYMBOL          | LIMIT       | UNIT |  |  |

| Drain-Source Voltage                                                         | V <sub>DS</sub> | 650         | V    |  |  |

| Drain-to-Source Voltage - transient (Note 1)                                 | VDS(transient)  | 850         | V    |  |  |

| Gate-Source Voltage                                                          | V <sub>GS</sub> | -10 to +7   | V    |  |  |

| Gate-to-Source Voltage - transient (Note 1)                                  | VGS(transient)  | -20 to +10  | V    |  |  |

| $T_c = 25^{\circ}C$                                                          | l <sub>DS</sub> | 30          |      |  |  |

| Continuous Drain Current T <sub>c</sub> = 100°C                              |                 | 20          | А    |  |  |

| Pulse Drain Current (Pulse width 10 $\mu$ s, V <sub>GS</sub> = 6 V) (Note 2) | DS Pulse        | 60          |      |  |  |

| Operating Junction Temperature                                               | TJ              | -55 to +150 | °C   |  |  |

| Storage Temperature Range                                                    | Ts              | -55 to +150 | °C   |  |  |

#### Notes:

1. For <u><</u> 100 μs.

2. Defined by product design and characterization.

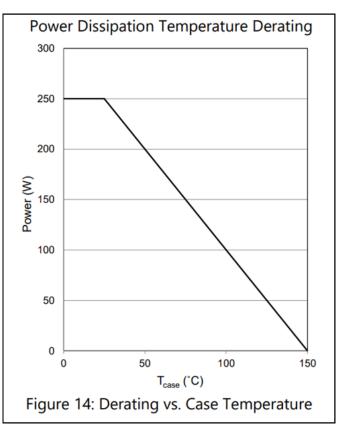

| THERMAL PERFORMANCE                            |                  |       |      |  |  |

|------------------------------------------------|------------------|-------|------|--|--|

| PARAMETER                                      | SYMBOL           | LIMIT | UNIT |  |  |

| Junction to Case Thermal Resistance            | Rejc             | 0.5   | °C/W |  |  |

| Junction to Ambient Thermal Resistance(Note 3) | R <sub>0JA</sub> | 35    | °C/W |  |  |

Notes:

3. Device mounted on 1.6 mm PCB thickness FR4, 4-layer PCB with 2 oz. copper on each layer. The recommendation for thermal vias under the thermal pad is 0.3 mm diameter (12 mil) with 0.635 mm pitch (25 mil). The copper layers under the thermal pad and drain pad are 25 x 25 mm2 each. The PCB is mounted in horizontal position without air stream cooling

| <b>Electrical Characteristics</b> (Typical values at $T_J = 25$ °C, $V_{GS} = 6$ V unless otherwise noted) |                                        |                     |     |     |     |      |

|------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------|-----|-----|-----|------|

| PARAMETER                                                                                                  | CONDITIONS                             | SYMBOL              | MIN | ТҮР | MAX | UNIT |

| Drain-to-Source Blocking Voltage                                                                           | Vgs = 0 V, Idss ≤ 58 µA                | V(BL)DSS            | 650 |     |     | V    |

| Gate Threshold Voltage                                                                                     | $V_{GS} = V_{DS}, I_D = 7.5 \text{mA}$ | V <sub>GS(TH)</sub> | 1.1 | 1.7 | 2.6 | V    |

| Gate-to-Source Current                                                                                     | Vgs = 6 V, Vds = 0 V                   | lgs                 |     | 182 |     | μA   |

| Drain-Source Leakage Current                                                                               | Vbs = 650 V, Vgs = 0 V<br>TJ = 25 °C   |                     |     | 2   | 58  | μA   |

|                                                                                                            | Vps = 650 V, Vgs = 0 V<br>Tj = 150 °C  | IDSS                |     | 70  |     |      |

| Drain-Source On-State Resistance                                                                           | Vgs = 6 V, TJ = 25 °C<br>Ids = 5.5 A   | R <sub>DS(on)</sub> |     | 50  | 68  | mΩ   |

|                                                                                                            | Vgs = 6 V, TJ = 150 °C<br>Ids = 5.5 A  |                     |     | 127 |     |      |

| Total Gate Charge                                                                                          | Vgs = 0 to 6 V                         | Qg                  |     | 6.7 |     |      |

| Gate-Source Charge                                                                                         |                                        | Qgs                 |     | 1.9 |     |      |

| Gate-Drain Charge                                                                                          | VDS = 400 V                            | Qgd                 |     | 2   |     | nC   |

| Output Charge                                                                                              | Vgs = 0 V, Vds = 400 V                 | Qoss                |     | 61  |     |      |

| Gate Plateau Voltage                                                                                       | VDS = 400 V,IDS = 30 A                 | Vplat               |     | 3.5 |     | V    |

| Internal Gate Resistance                                                                                   | f = 5 MHz, open drain                  | RG                  |     | 1.3 |     | Ω    |

| Input Capacitance                                                                                          | VDS = 400 V                            | Ciss                |     | 235 |     |      |

| Output Capacitance                                                                                         | Vgs = 0 V                              | Coss                |     | 60  |     |      |

| Reverse Transfer Capacitance                                                                               | f = 100 kHz                            | Crss                |     | 0.6 |     |      |

| Effective Output Capacitance<br>Energy Related (Note 4)                                                    | Vgs = 0 V                              | C <sub>O(ER)</sub>  |     | 96  |     | pF   |

| Effective Output Capacitance<br>Time Related (Note 5)                                                      | Vps = 0 to 400 V                       | Co(tr)              |     | 150 |     |      |

| Reverse Recovery Charge                                                                                    |                                        | Qrr                 |     | 0   |     | nC   |

#### Notes:

- 4. C<sub>O(ER)</sub> is the fixed capacitance that would give the same stored energy as Coss while V<sub>DS</sub> is rising from 0 V to the stated V<sub>DS</sub>.

- 5. Co(TR) is the fixed capacitance that would give the same charging time as Coss while VDs is rising from 0 V to the stated VDs.

# TSG65N068CE

**Taiwan Semiconductor**

| <b>Electrical Characteristics cont'd</b> (Typical values at $T_J = 25$ °C, $V_{GS} = 6$ V unless otherwise noted) |                                                          |                     |      |      |     |      |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------|------|------|-----|------|

| PARAMETER                                                                                                         | CONDITIONS                                               | SYMBOL              | MIN  | ТҮР  | МАХ | UNIT |

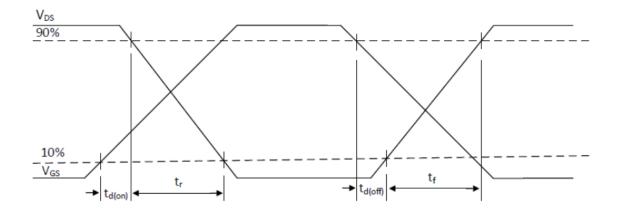

| Turn-On Delay                                                                                                     | Vdd = 400 V,                                             | t <sub>D(on)</sub>  |      | 8.2  |     |      |

| Rise Time                                                                                                         | Vgs = +6/-3 V,                                           | t <sub>R</sub>      |      | 6.3  |     |      |

| Turn-Off Delay                                                                                                    | Ibs = 15 A,                                              | t <sub>D(off)</sub> |      | 10.8 |     | nS   |

| Turn-Off Fall Time                                                                                                | $= R_{G(on)} = 15 \Omega,$<br>$= R_{G(off)} = 2 \Omega,$ | tF                  |      | 5.7  |     |      |

| Switching Energy during turn-on                                                                                   | $L = 90 \mu\text{H}, LP = 12 \text{nH}$                  | Eon                 |      | 50   |     |      |

| Switching Energy during turn-off                                                                                  | (Notes 6 , 7, 8)                                         | Eoff                |      | 10   |     | μJ   |

| Output Capacitance Stored                                                                                         | VDS = 400 V                                              | Eoss                | Fase | 8    |     | μυ   |

| Energy                                                                                                            | Vgs = 0 V, f = 100 kHz                                   | LOSS                |      | 0    |     |      |

Notes:

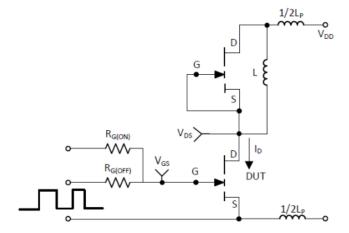

- 6. See Figure 16 for switching test circuit diagram.

- 7. See Figure 17 for switching time definition waveforms.

- 8. LP = parasitic inductance

#### **ORDERING INFORMATION**

| ORDERING CODE   | PACKAGE | PACKING             |

|-----------------|---------|---------------------|

| TSG65N068CE RVG | PDFN88  | 3,000pcs / 13" Reel |

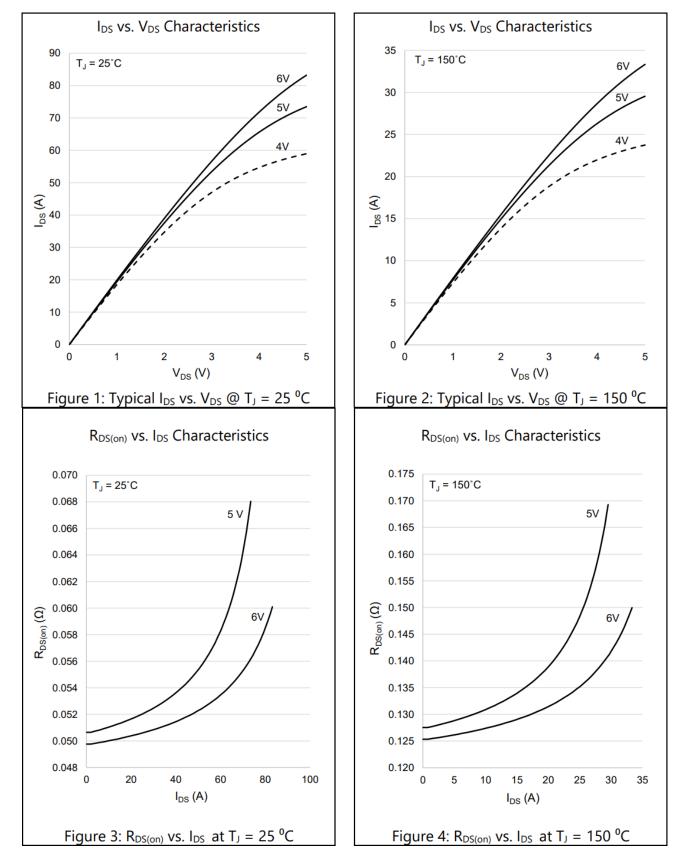

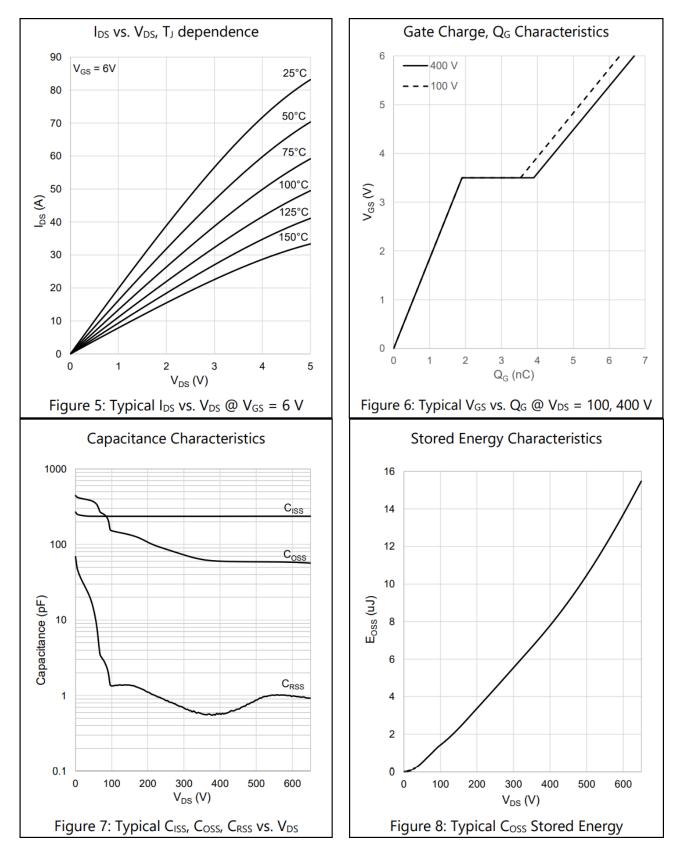

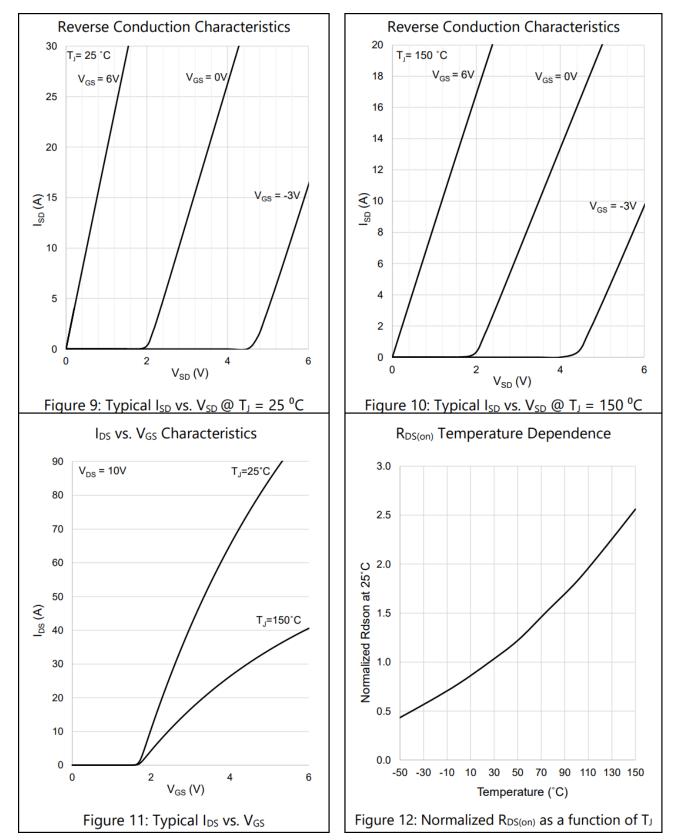

## **Electrical Performance Graphs**

# **Electrical Performance Graphs**

## **Electrical Performance Graphs**

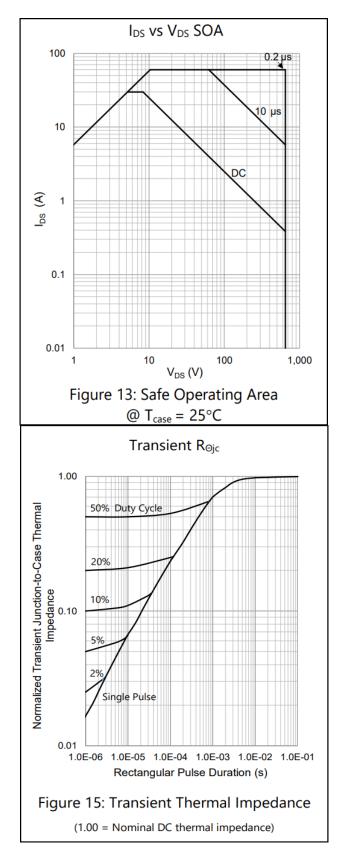

# **Thermal Performance Graphs**

# **Test Circuits**

Figure 16: Switching Test Circuit

### PACKAGE OUTLINE DIMENSIONS (Unit: Millimeters)

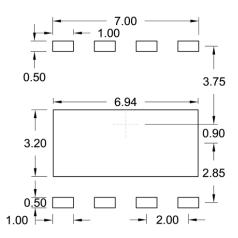

### **Recommended PCB Footprint**

### **MARKING DIAGRAM**

TSC G65N068 YWWLF

Y= Year CodeWW= Week Code (01~52)L= Lot Code (1~9,A~Z)F= Factory Code

# TSG65N068CE

Taiwan Semiconductor

## Notice

Specifications of the products displayed herein are subject to change without notice. TSC or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Purchasers are solely responsible for the choice, selection, and use of TSC products and TSC assumes no liability for application assistance or the design of Purchasers' products.

Information contained herein is intended to provide a product description only. No license, express or implied, to any intellectual property rights is granted by this document. Except as provided in TSC's terms and conditions of sale for such products, TSC assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of TSC products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify TSC for any damages resulting from such improper use or sale.