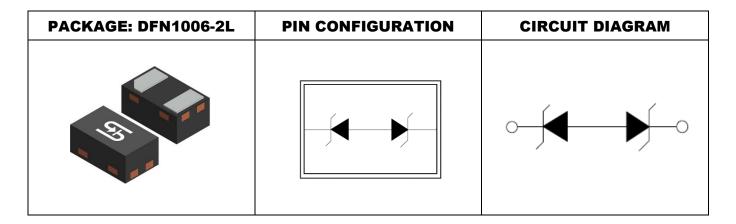

## **Bi-directional ESD Protection Diode**

#### **DESCRIPTIONS**

The TESDL24VB17P1Q1 is Bidirectional ESD rated clamping cell to protect power interfaces, or control line, or low speed data line in an electronic system. It has been specifically designed to protect sensitive electronic components which are connected to power and control lines from over-voltage damage by Electrostatic Discharging (ESD), and Lightning.

TESDL24VB17P1Q1 is a unique design which includes proprietary clamping cells in a small package. During transient conditions, the proprietary clamping cells prevent over-voltage on the control/data/power lines, protecting any downstream components.

The TESDL24VB17P1Q1 may be used to provide ESD protection up to ±30kV(contact and air discharge) according to IEC61000-4-2, and withstand peak pulse current up to 3A(8/20µs) according to IEC61000-4-5.

#### **FEATURES**

- ESD protect for 1 line with bidirectional.

- Provide ESD protection for each channel to IEC61000-4-2 (ESD) ±30kV (air), ±30kV (contact) IEC61000-4-4 (EFT) 4kV (5/50ns) IEC61000-4-5 (Lightning) 3A (8/20µs)

- Suitable for 24V and below, operating voltage applications

- Protect I/O line or power line.

- Moisture sensitivity level: level 1, per J-STD-020

- RoHS Compliant

- Halogen-Free

#### **APPLICATION**

- General Purpose I/O

- Portable Instrumentation

- Power lines on PCB Protection

1

Taiwan Semiconductor

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25°C unless otherwise noted) |                  |             |      |  |  |  |  |

|-------------------------------------------------------------------------|------------------|-------------|------|--|--|--|--|

| PARAMETER                                                               | SYMBOL           | VALUE       | UNIT |  |  |  |  |

| Peak pulse power (tp = 8/20us)                                          | Ррк              | 150         | W    |  |  |  |  |

| Peak pulse current (tp = 8/20us)                                        | <b>I</b> PP      | 3           | А    |  |  |  |  |

| ESD according to IEC61000-4-2 air discharge                             | Vesp             | ±30         | kV   |  |  |  |  |

| ESD according to IEC61000-4-2 contact discharge                         | VESD             | ±30         | kV   |  |  |  |  |

| Junction temperature range                                              | TJ               | -55 to +125 | °C   |  |  |  |  |

| Storage temperature range                                               | T <sub>STG</sub> | -55 to +125 | °C   |  |  |  |  |

| ELECTRICAL SPECIFICATIONS (T <sub>A</sub> = 25°C unless otherwise noted) |                                             |                  |      |      |      |      |  |

|--------------------------------------------------------------------------|---------------------------------------------|------------------|------|------|------|------|--|

| PARAMETER                                                                | CONDITIONS                                  | SYMBOL           | MIN  | TYP  | MAX  | UNIT |  |

| Reverse working voltage                                                  |                                             | V <sub>RWM</sub> | -    | -    | 24   | V    |  |

| Reverse breakdown voltage                                                | I <sub>R</sub> = 1mA, T <sub>J</sub> = 25°C | V <sub>BR</sub>  | 25.2 | -    | 32.6 | V    |  |

| Reverse leakage current                                                  | V <sub>RWM</sub> = 24V                      | I <sub>R</sub>   | -    | -    | 50   | nA   |  |

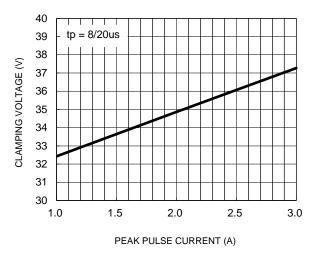

| Clamping voltage <sup>(1)</sup>                                          | $I_{PP} = 3A$ , $tp = 8/20us$               | Vc               | -    | -    | 50   | V    |  |

| Clamping voltage <sup>(2)</sup>                                          | I <sub>TLP</sub> = 2A, tp = 100ns           | V                | -    | 31   | -    | V    |  |

|                                                                          | $I_{TLP} = 8A, tp = 100ns$                  | V <sub>CL</sub>  | -    | 33.7 | -    | V    |  |

| Junction capacitance                                                     | $1MHz, V_R = 0V$                            | Сл               | -    | 13.9 | 17.5 | pF   |  |

| Dynamic resistance <sup>(2)</sup>                                        | •                                           | R <sub>DYN</sub> | -    | 0.45 | -    | Ω    |  |

## Notes:

- 1. Non-repetitive current pulse, according to IEC61000-4-5.

- 2. TLP parameter:  $Z_0$  = 50  $\Omega$ , tp = 100ns, tr = 2ns, averaging window from 60ns to 80ns. RDYN is calculated from 2A to 8A.

| ORDERING INFORMATION |            |                         |  |  |  |

|----------------------|------------|-------------------------|--|--|--|

| ORDERING CODE        | PACKAGE    | PACKING                 |  |  |  |

| TESDL24VB17P1Q1 RNG  | DFN1006-2L | 10,000 / 7" Tape & Reel |  |  |  |

2

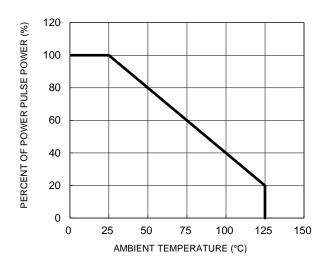

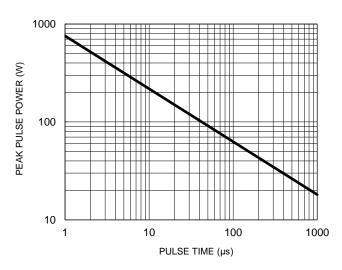

### **CHARACTERISTICS CURVES**

(T<sub>A</sub> = 25°C unless otherwise noted)

Fig.1 Peak Pulse Power vs. Junction Temperature Fig.2 Non-Repetitive Peak Pulse Power vs. Pulse Time

Fig.3 Clamping Voltage vs. Peak Pulse Current

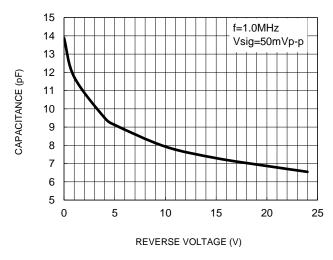

Fig.4 Capacitance vs. Reverse Voltage

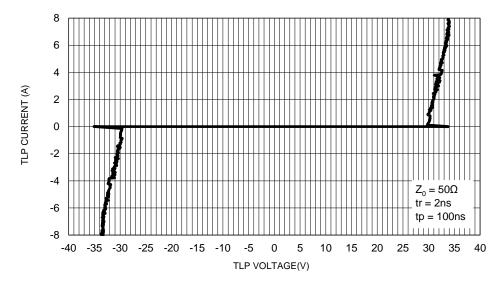

Fig.5 TLP Curve

## **CHARACTERISTICS CURVES**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

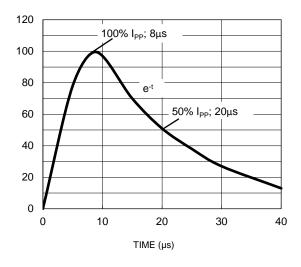

Fig.6 8/20µs pulse waveform per IEC61000-4-5

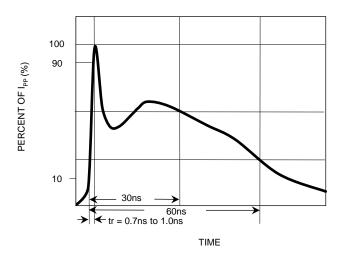

Fig.7 ESD pulse waveform per IEC61000-4-2

Version: A2403

4

### **PACKAGE OUTLINE DIMENSIONS**

# **DFN1006-2L** 0.675 0.550 I /3\ II /4\ III /4\ В 1.075 A 0.950 NO TIE BAR 0.53 0.34 TIE BAR 0.05 TIE BAR OPTION C 0.00 **CORNER** SEATING PLANE **NOTCH OPTION /**4\ 0.55 0.45 /3\ I Ш ⊕ 0.05 M C A B 0.75 -0.60 0.30 0.20 0.65 **←** 0.45 **←** SUGGESTED PAD

MARKING DIAGRAM

AE = MARKING CODE

NOTES: UNLESS OTHERWISE SPECIFIED

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3 CATHODE TERMINAL MAY HAVE CHAMFER, NOTCH OR FULL 90 DEGREES CORNER.

- 4 TERMINAL EDGE MAY HAVE TIE BAR OR NONE.

**LAYOUT**

- 5. SUGGESTED PAD LAYOUT IS FOR REFERENCE PURPOSE ONLY.

- 6. DWG NO. REF: HQ2SD07-DFN1006\_2L-075 REV A.

Taiwan Semiconductor

### **Notice**

Specifications of the products displayed herein are subject to change without notice. TSC or anyone on its behalf assumes no responsibility or liability for any errors or inaccuracies.

Purchasers are solely responsible for the choice, selection, and use of TSC products and TSC assumes no liability for application assistance or the design of Purchasers' products.

Information contained herein is intended to provide a product description only. No license, express or implied, to any intellectual property rights is granted by this document. Except as provided in TSC's terms and conditions of sale for such products, TSC assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of TSC products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify TSC for any damages resulting from such improper use or sale.